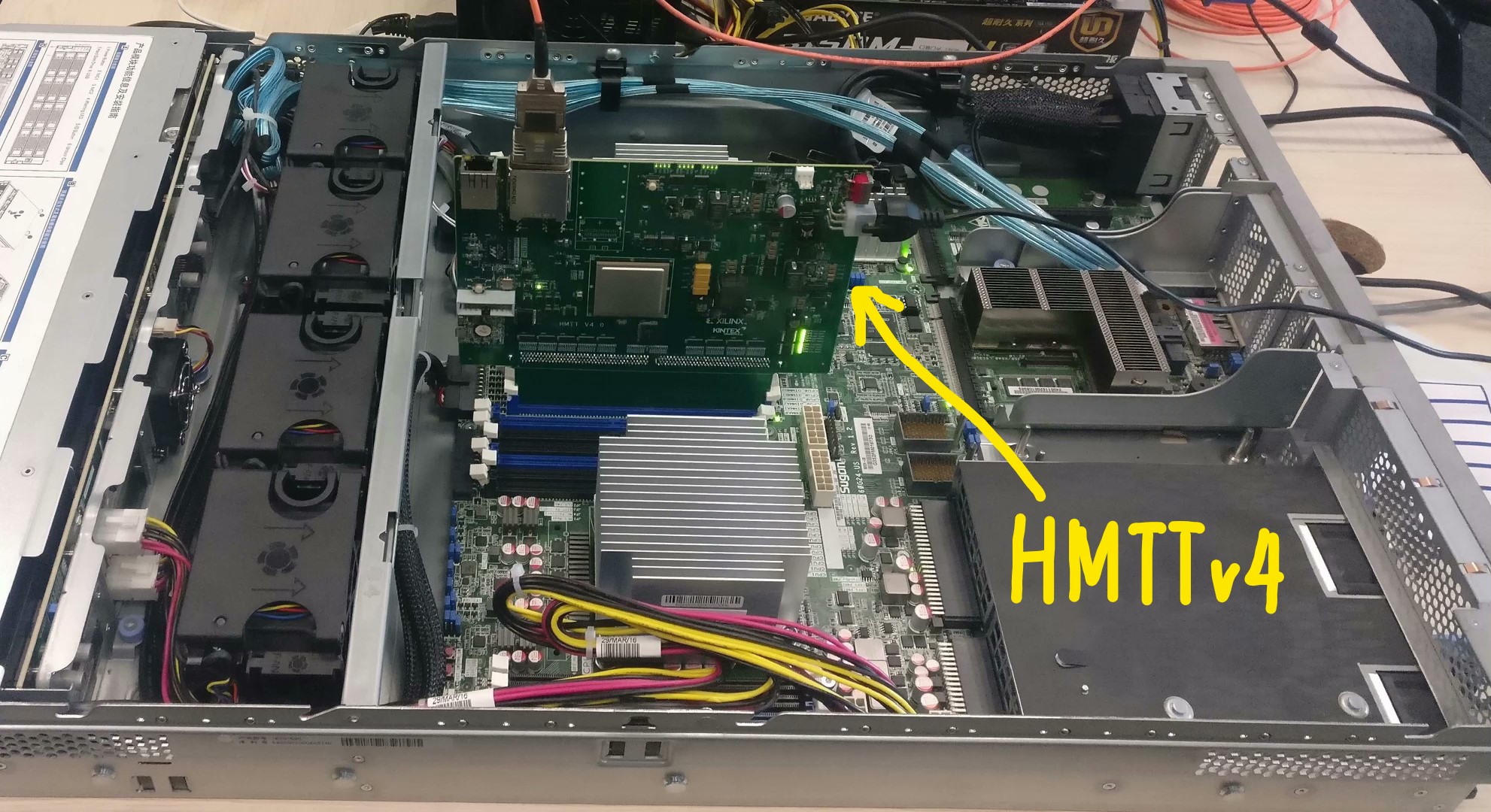

Photo: HMTTv4 on a server collecting traces of DDR4 address and data

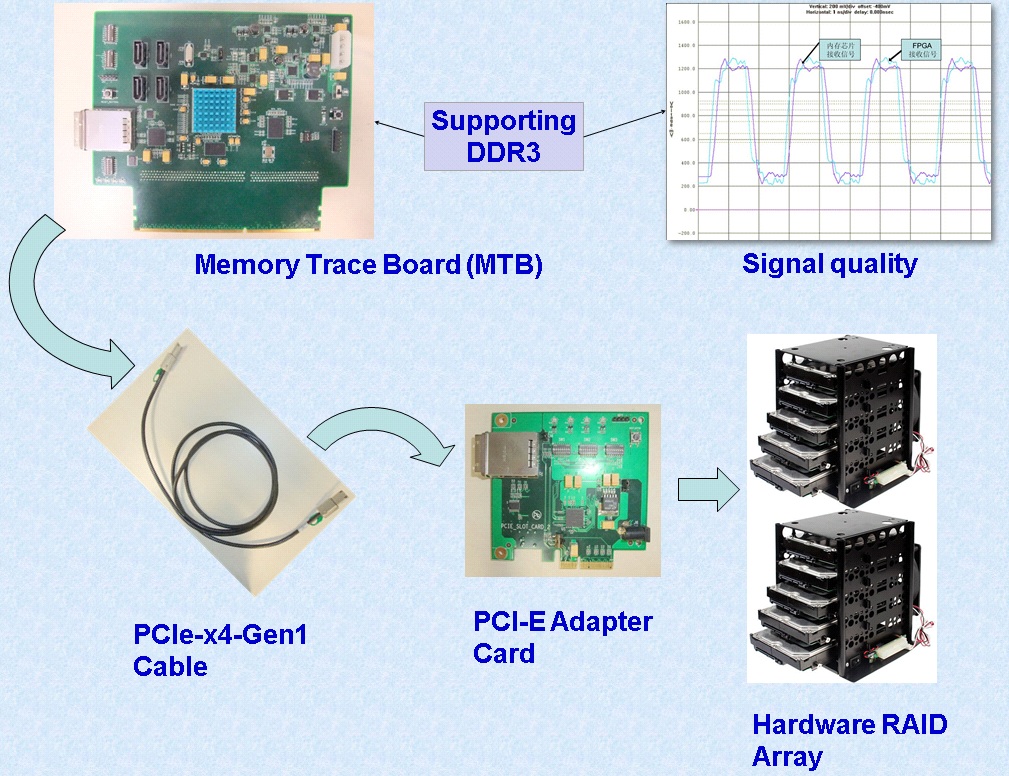

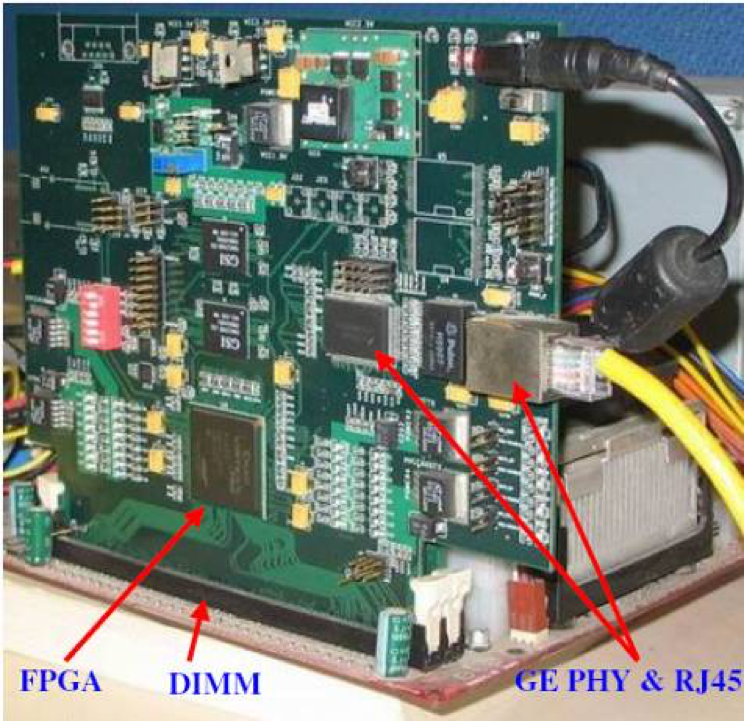

HMTT was my Ph.D. project supervised by Prof. Mingyu Chen who is leading a lab of ACS and has been keeping building more advanced HMTT over the past decade. Currently, there are two versions: HMTTv3 supports DDR3-800/1600 and HMTTv4 supports DDR4. HMTT can provide off-chip memory traces of many real-world applications, e.g., SPECCPU, SPECjbb, TPC-H/TPC-C on Oracle, and SPECWeb on Apache, with abundant important information, such as timestamp, pid, cpu-request/io-request, r/w, virt_addr and phys_addr.

3/2019: A demo vedio of HMTT.

2/2018: HMTTv4 that can collect traces of both address and data on DDR4 bus released. Contact Prof. Mingyu Chen for more details.

4/2016: HMTTv3 was updated to support DDR3-1333.

10/2015: HMTTv3 was deployed in Huawei Research Lab. [working photo]

4/2014: A paper on characterizing VMs' memory accesses was published on VEE.

2/2014: A summary paper was published on TACO.

2/2013: HMTT Tutorial @ HPCA 2013 [slides]

9/2012: A lightway lock profiling tool w/ HMTT was published on PACT.

4/2012: HMTT was able to distinguish objects' memory access, published on ISPASS.

2/2010: HMTT collected DMA traces for I/O access optimization, published on HPCA.

6/2008: The first paper on HMTT was published on SIGMETRICS.