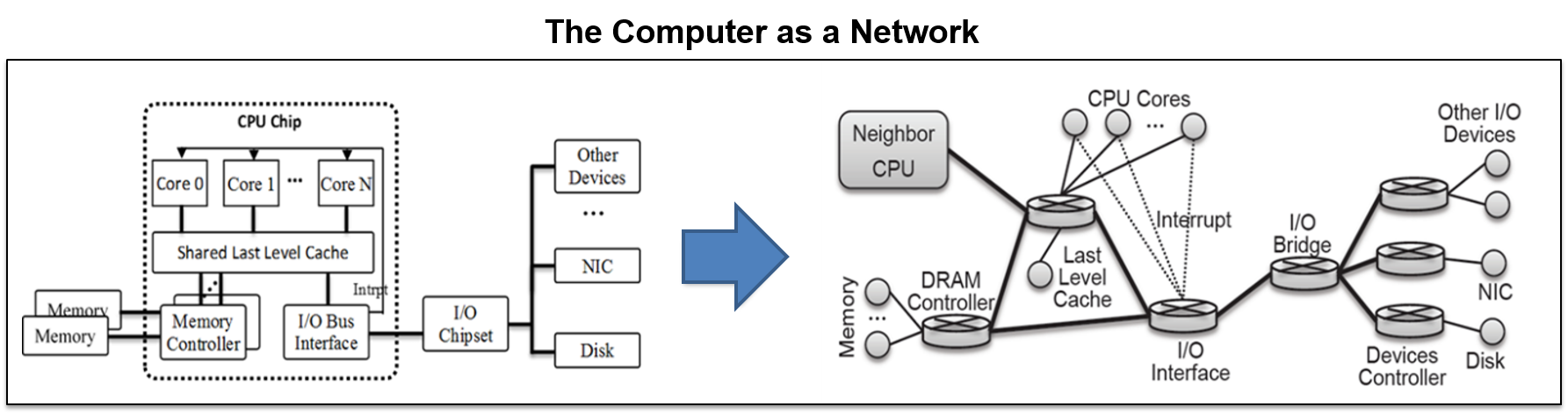

Step-1: View a computer as a network

Step-2: Reconstruct a computer as a software-defined network (SDN)

Based on the insight of Computer as a Network, this project investigates architectural support for managing and controlling shared hardware resources, which impose significant challenges on warehouse-scale datacenters and real-time systems. LvNA enables a new hardware/software interface by introducing a hardware labeling mechanism to convey software's semantic information such as QoS and security to the underlying hardware. LvNA is able to correlate hardware labels with various entities (e.g., virtual machine, process and thread), propagate labels in the whole datapaths and program differentiated services rules based on labels. We have implemented a RISC-V based FPGA prototype (a.k.a. Labeled RISC-V) that has been already open-sourced: https://github.com/LvNA-system/labeled-RISC-V.

6/2019: I was invited to give a talk on open-source chip ecosystem at SIGARCH Visioning Workshop co-located with ISCA 2019. [slides]

4/2019: A paper on controling QoS of SMT processor got accepted to ICS.

4/2019: A paper on analysis of Alibaba's datacenter traces got accepted to IWQoS.

3/2019: A demo vedio of open sourced Labeled RISC-V Cluster.

10/2018: A turorial will be held at MICRO'2018[Tutorial Page]

9/2018: I was invited to give a keynote presentation at ARM Research Summit 2018: The Case for Labeled Computer Architecture.

7/2018: The FlameCluster prototype works -- a cluster of eight Labeled RISC-V nodes that can run Redis, Xapian etc. FlameCluster can enforce end-to-end performance isolation through labeled HW/SW co-design including labeled SoC, labeled container, labeled Ceph and labeled TCP/IP stack.

6/2018: A turorial was held at ISCA'2018[Tutorial Page]

11/2017: Project progress was presented at the 7th RISC-V workshop[slides] [video]

11/2017: A collaborative work with Princeton University got published on ICCD.

10/2017: A paper on LvNA was presented at the CARRV workshop co-located with MICRO.

5/2017: Labeled RISC-V was presented at the 6th RISC-V workshop. [slides][video]

5/2017: An open-source Labeled RISC-V RTL released: https://github.com/fsg-ict/labeled-RISC-V

2/2017: A position paper on Labeled von Neumann Architecture was published.

7/2016: Received a five-year funding of ~$4M from the Ministry of Science and Technology (MOST).

6/2016: The open-sourced FPGA-based PARD prototype released at ISCA 2016: CaaN Tutorial

10/2015: Invited to parcipate in Dastughl Seminar on "Rack-Scale Computing": Dastuhl Seminar

3/2015: Presentation at ASPLOS'15: pard-asplos15-slides.pdf

1/2015: GEM5-based full-system PARD simulator was open sourced: Github

11/2014: Our first paper on PARD is accepted by ASPLOS'15 (ranked #8 of ~280 submissions).

10/2012: Yungang returned back to ICT from Princeton University and started a new project: Programmable Architecture for Resourcing-on-Demand (PARD) .